# UNIVERSIDAD NACIONAL DE CÓRDOBA

# FACULTAD DE CIENCIAS EXACTAS, FÍSICAS Y NATURALES CARRERA INGENIERÍA ELECTRÓNICA

# PROYECTO INTEGRADOR PARA LA OBTENCIÓN DEL TÍTULO DE GRADO INGENIERO ELECTRÓNICO

### "DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR"

Alumno: Banchio, Agustín Enrique

Director: Ing. Rodrigo Bruni

Co-Director: Ing. José Amado

# UNIVERSIDAD NACIONAL DE CÓRDOBA

FACULTAD DE CIENCIAS EXACTAS, FÍSICAS Y NATURALES

CARRERA INGENIERÍA ELECTRÓNICA

# PROYECTO INTEGRADOR PARA LA OBTENCIÓN DEL TÍTULO DE GRADO INGENIERO ELECTRÓNICO

### "DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR"

Alumno: Banchio, Agustín Enrique

Director: Ing. Rodrigo Bruni

Co-Director: Ing. José Amado

Córdoba, República Argentina – 2017

# UNIVERSIDAD NACIONAL DE CÓRDOBA

#### Facultad de Ciencias Exactas, Físicas y Naturales

### Escuela de Ingeniería Electrónica

El Tribunal Evaluador reunido en éste acto y luego de haber aprobado la Solicitud de Aprobación de Tema y efectuado las distintas instancias de correcciones del Informe del Proyecto Integrador para la obtención del Título de Grado "Ingeniero Electrónico" y cumpliendo con el Reglamento correspondiente, declaran el Informe Final de/l los estudiante/s: **Agustín Enrique Banchio** como "aceptado sin correcciones" y la defensa oral Aprobada. Por lo tanto, luego de haber tenido en cuenta los aspectos de evaluación que indica el Reglamento, el Proyecto Integrador se considera Aprobado.

Se firma el Acta de Examen correspondiente y se distribuyen los ejemplares impresos.

| Firma y aclaración del Tribunal Evaluado |

|------------------------------------------|

| Fecha:                                   |

| NOTA:                                    |

BANCHIO, Agustín Enrique

# **Agradecimientos**

A mi familia por el apoyo que me brindaron durante cursado completo de la carrera.

A mis compañeros y amigos por todos los momentos que compartimos.

A mis profesores por enseñarme y formarme en esta profesión.

Al director y co-director de este proyecto, por su tiempo y dedicación.

### Resumen

Los receptores de radio convencionales, como los utilizados generalmente en televisores y receptores de radiofonía, permiten recuperar la información contenida en la señal recibida mediante un circuito específico acorde a la modulación de la señal que se desea demodular.

Una alternativa a los circuitos de recepción tradicionales anteriormente descriptos consiste en el acondicionamiento y digitalización de la señal recibida. La recuperación de la información se realiza por medio de algoritmos de procesamiento de señales. Este sistema es conocido como radio definida por software (SDR) y provee más versatilidad comparado al hardware.

Este trabajo consiste en el diseño e implementación de un front end analógico para SDR (bloque de cadena de recepción encargado de filtrar, amplificar y trasladar en frecuencia la señal).

Adicionalmente se incorpora al diseño la etapa de conversión analógica digital, y como dispositivo de control un microcontrolador encargado tanto del manejo del equipo como de la comunicación con una PC, donde la señal recibida es procesada digitalmente.

El procesamiento es realizado mediante un bloque de programa basado en el software libre GNU Radio. La aplicación además es la encargada de enviar la información para la selección del ancho de banda y frecuencias de trabajo al dispositivo.

### Área Temática y Asignaturas

Área temática: Comunicaciones

Asignaturas: Electrónica Analógica III, Teoría de las comunicaciones, Electrónica

Digital III

#### **Palabras Claves**

Front End, Radio Definida por Software, Receptor, Superheterodino, Microcontrolador

#### **Abstract**

Conventional radio receivers, such as those commonly used in televisions and audio broadcasting, allow information contained in the received signal to be recovered using a circuit specifically designed according to the modulation of the signal to be demodulated. An alternative to the previously described reception circuits consists of the conditioning and digitalization of the received signal. The recovery of information is done with signal processing algorithms. This system is known as software defined radio (SDR) and provides

If instead of utilizing a specific circuit, the received signal is digitalized and sent to a PC capable of processing it, this information can be recovered with signal processing algorithms. This system is known as software defined radio and provides more versatility compared to hardware solutions.

This project consists of the design and implementation of an analog front end for SDR (block of the reception chain responsible for filtering, amplifying and transferring the signal).

Additionally, the analog to digital conversion stage is incorporated into the design, and as a control device, a microcontroller is added for both the handling of the components configuration and the communication with the PC, where the received signal is digitally processed.

The processing is done through a program blocked based on the free software GNU Radio. The application is also responsible for sending the information for the bandwidth and tuning settings of the device.

#### **Key Words**

Front End, Software Defined Radio, Receiver, Superheterodyne, Microcontroller

# Índice

| Resumen                                              | VII   |

|------------------------------------------------------|-------|

| Área Temática y Asignaturas                          | VI    |

| Palabras Claves                                      | VII   |

| Abstract                                             | IX    |

| Key Words                                            | IX    |

| Índice                                               | XI    |

| Lista de Tablas                                      | XVII  |

| Lista de Figuras                                     | XIX   |

| Lista de Símbolos y Convenciones                     | XXIII |

| Símbolos                                             | XXIII |

| Abreviaciones                                        | XXIII |

| Introducción                                         | 1     |

| 1.1 Objetivos                                        | 1     |

| 1.1.1 Objetivo General                               | 1     |

| 1.1.2 Objetivos específicos                          | 1     |

| 1.2 Antecedentes                                     | 1     |

| 1.3 Motivación                                       | 2     |

| 1.4 Metodología para lograr los objetivos propuestos | 2     |

| 1.5 Plan del proyecto                                | 2     |

| Radiocomunicaciones                                  | 5     |

| 2.1 Radiocomunicación                                | 5     |

| 2.2 Espectro Radioeléctrico                          | 5     |

| 2.3 Modulación                                            | 7  |

|-----------------------------------------------------------|----|

| 2.4 Receptor de Radio                                     | 9  |

| Componentes de un receptor de radio                       | 11 |

| 2.4.1 Antena                                              | 11 |

| 2.4.2 Amplificador de radiofrecuencia                     | 11 |

| 2.4.2.1 Parámetros de un amplificador de radiofrecuencia  | 11 |

| 2.4.3 Mezclador                                           | 12 |

| 2.4.3.1 Frecuencia Imagen                                 | 13 |

| 2.4.3.2 Parámetros de un mezclador                        | 14 |

| 2.4.4 Oscilador Local                                     | 15 |

| 2.4.4.1 Tipos de osciladores locales                      | 15 |

| 2.4.5 Filtros                                             | 16 |

| 2.4.5.1 Tipos de filtros según su tecnología              | 16 |

| 2.4.5.2 Tipos de filtros según su respuesta en frecuencia | 17 |

| 2.4.5.3 Rechazo de frecuencia imagen                      | 17 |

| 2.4.6 Demodulador                                         | 18 |

| 2.4.6.1 Ejemplos de técnicas de demodulación              | 18 |

| 2.5 Radio definida por software                           | 18 |

| 2.5.1 Conversor analógico digital                         | 19 |

| 2.5.1.1 Arquitecturas de conversores analógicos digitales | 19 |

| 2.5.1.2 Parámetros de un conversor analógico digital      | 20 |

| Microcontroladores y comunicación con PC                  | 21 |

| 3.1 Microcontrolador                                      | 21 |

| 3.1.1 Periféricos y Entradas/Salidas                      | 21 |

| 3.1.2 Interrupciones                                      | 22 |

| 3.2 Comunicación USB                                      | 22 |

|                                                           |    |

| 3.2.1 Protocolo de comunicación                             | 23 |

|-------------------------------------------------------------|----|

| 3.3 Ringbuffers                                             | 23 |

| Desarrollo del proyecto                                     | 25 |

| 4.1 Descripción general del proyecto                        | 25 |

| 4.1.1 Diagrama de Bloques General                           | 26 |

| 4.2 Acondicionamiento analógico                             | 27 |

| 4.2.1 Arquitectura del receptor                             | 27 |

| 4.2.2 Osciladores                                           | 28 |

| 4.2.3 Mezcladores                                           | 29 |

| 4.2.4 Amplificadores                                        | 31 |

| 4.2.5 Filtros                                               | 35 |

| 4.2.5.1 Filtro de la etapa de RF                            | 36 |

| 4.2.5.2 Filtro de la etapa de IF                            | 40 |

| 4.2.5.3 Filtro de la etapa de banda base                    | 41 |

| 4.2.5.4 Filtro de salida de osciladores                     | 42 |

| 4.2.6 Alimentación                                          | 44 |

| 4.3 Etapa de microcontrolador y digitalización              | 45 |

| 4.3.1 Microcontrolador                                      | 45 |

| 4.3.2 Conversor Analógico-Digital (ADC):                    | 48 |

| 4.3.3 Programación de microcontrolador:                     | 48 |

| 4.3.3.1 Diagrama en bloques del código del microcontrolador | 49 |

| 4.3.3.2 Muestreo                                            | 49 |

| 4.3.3.3 Configuración de osciladores                        | 50 |

| 4.3.3.4 Recibiendo la configuración de la PC                | 52 |

| 4.4 Diseño de driver en PC                                  | 53 |

| 4.4.1 Utilizando el puerto serie (virtual)                  | 53 |

| 4.4.2 Bloque de GNU Radio                                   | 53   |

|-------------------------------------------------------------|------|

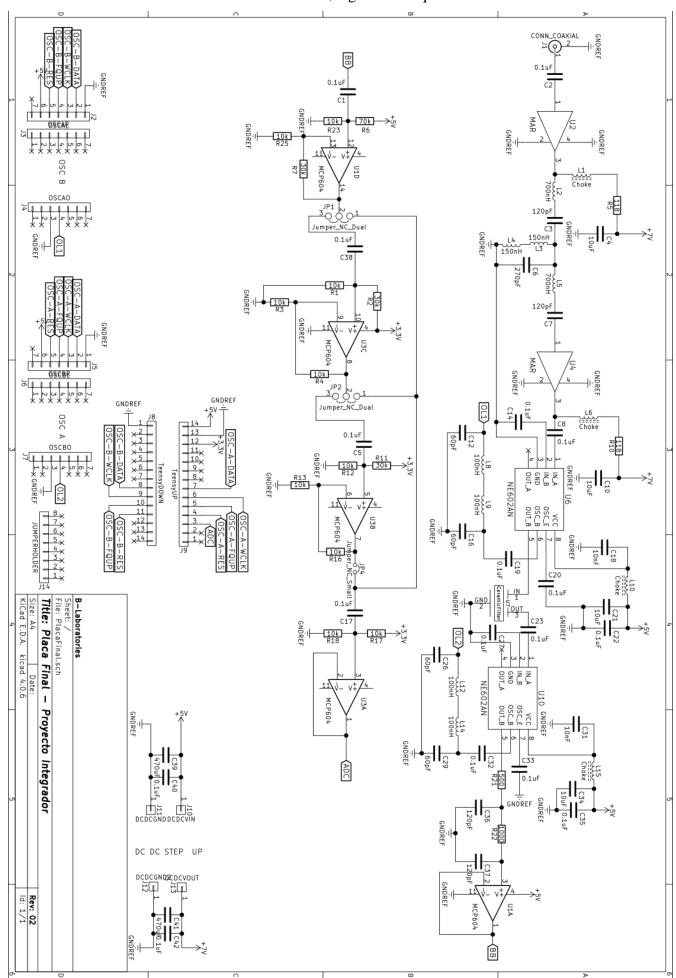

| 4.5 Circuito Final                                          | . 57 |

| Pruebas Realizadas                                          | 61   |

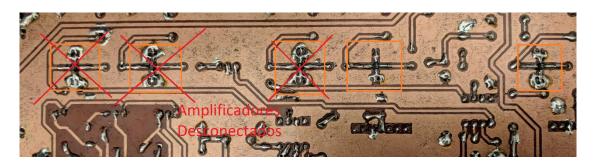

| 5.1 Pruebas Iniciales                                       | . 61 |

| 5.2 Pruebas del circuito final                              | . 63 |

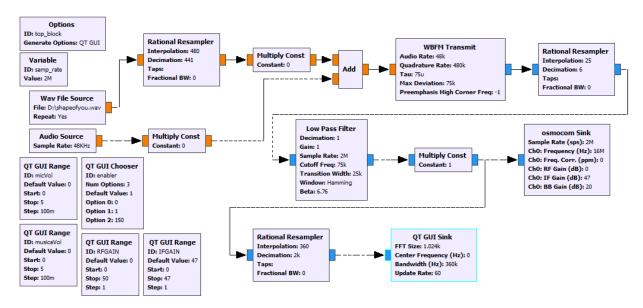

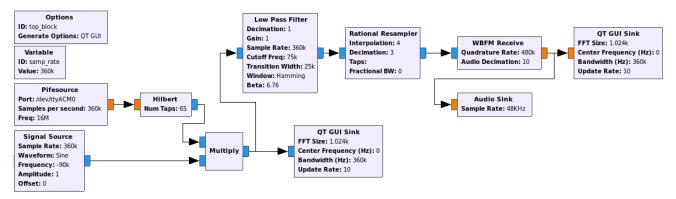

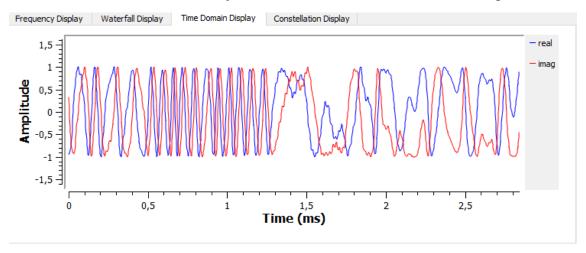

| 5.2.1 Prueba de modulación analógica                        | . 64 |

| 5.2.2 Prueba de modulación digital                          | . 67 |

| 5.2.3 Resultados                                            | . 70 |

| 5.2.4 Prueba de sensibilidad                                | . 70 |

| Instrucciones de uso                                        | 73   |

| 6.1 Consideraciones Preliminares                            | . 73 |

| 6.1.1 Reglas UDEV                                           | 73   |

| 6.2 Configuración de la placa                               | . 74 |

| 6.3 Utilización con GNU Radio                               | . 74 |

| 6.3.1 Instalación de paquetes necesarios                    | 75   |

| 6.3.2 Creación de módulo de GNU Radio                       | . 77 |

| 6.3.3 Creación del bloque de GNU Radio                      | . 77 |

| 6.3.4 Compilación e Instalación del bloque                  | . 78 |

| 6.4 Utilización fuera de GNU Radio                          | . 80 |

| Conclusiones                                                | 81   |

| 7.1 Resultados obtenidos en base a los objetivos propuestos | . 81 |

| 7.2 Conclusión General                                      | . 82 |

| 7.3 Mejoras a futuro                                        | . 83 |

| Bibliografía y Referencias                                  | 85   |

| Anexo 1: Circuito final implementado                        | 87   |

| Anexo 2: Código de microcontrolador                         | 89   |

| BANCHIO, | Agustín | Enriq | ue |

|----------|---------|-------|----|

|----------|---------|-------|----|

| Anexo 3: Código de bloque de GNU Radio | 95  |

|----------------------------------------|-----|

| Solicitud de Aprobación de Tema        | 99  |

| Nota de aprobación                     | 106 |

| $\mathbf{T}$ | •         | 4  | 1                      |     |     | 1    |

|--------------|-----------|----|------------------------|-----|-----|------|

|              | 10        | ta | de                     | 1 9 | h   | 20   |

|              | $^{11}$ 5 | ua | $\mathbf{u}\mathbf{v}$ | 14  | 1/1 | 1415 |

| Tabla 1 – Bandas de espectro radioeléctrico según UIT |    |

|-------------------------------------------------------|----|

|                                                       |    |

| Tabla 2 – Especificaciones de Teensy 3.2              | 47 |

# Lista de Figuras

| Figura 1 – Utilización comercial de bandas del espectro radioeléctrico                   |

|------------------------------------------------------------------------------------------|

| Figura 2 - Representación gráfica de las ondas moduladas en AM y FM, junto a las         |

| señales portadora y modulante                                                            |

| Figura 3 – 4 Símbolos de modulación ASK                                                  |

| Figura 4 – Diagrama de bloques de receptor superheterodino                               |

| Figura 5 – Diagramas de bloques de distintos receptores de radios definidas por software |

|                                                                                          |

| Figura 6 – Representación simbólica de un mezclador                                      |

| Figura 7 – Representación de conversión descendente y conversión ascendente 13           |

| Figura 8 – Representación en frecuencia de frecuencia imagen respecto a frecuencia del   |

| oscilador y de la señal deseada                                                          |

| Figura 9 – Diagrama de bloques de un oscilador PLL                                       |

| Figura 10 – Diagrama de bloques de oscilador de síntesis digital directa 16              |

| Figura 11 – Ringbuffer con los punteros de lectura y escritura                           |

| Figura 12- Diagrama de bloques del proyecto                                              |

| Figura 13 – Receptor superheterodino de doble conversión                                 |

| Figura 14 - Placa de desarrollo del sintetizador AD9850                                  |

| Figura 15 – Diagrama de bloques del NE602AN                                              |

| Figura 16 – NE602AN empaquetado DIP                                                      |

| Figura 17 – Circuito Equivalente del NE602AN                                             |

| Figura 18 – Amplificadores MAR-1 (izquierda) y MAR-3 (Derecha)                           |

| Figura 19 - Circuito recomendado de aplicación de amplificadores MAR según               |

| fabricante. 32                                                                           |

| Figura 20 – MCP6294 encapsulado DIP                                                      |

| Figura 21 – Amplificación de la señal sin sufrir distorsión por corte o saturación 34    |

| Figura 22 - Circuito que filtra la señal continua, le suma un cuarto de la tensión de    |

| alimentación y amplifica por dos                                                         |

| Figura 23 – Señal filtrada y desplazada al centro del rango del ADC                      |

| Figura 24 – Circuito que filtra la señal y le suma la mitad de la tensión de referencia |

|-----------------------------------------------------------------------------------------|

| incluyendo un buffer previo al ADC                                                      |

| Figura 25 – Diagrama esquemático del filtro de la etapa de RF                           |

| Figura 26 – Diagrama de Bode del filtro de la etapa de RF                               |

| Figura 27 – Respuesta del filtro según simulación                                       |

| Figura 28 – Respuesta de mediciones del filtro junto a un amplificador MAR-3+ 39        |

| Figura 29 – Filtro cerámico SFELF10M7HAA0-B0                                            |

| Figura 30 – Respuesta del filtro cerámico                                               |

| Figura 31 – Diagrama esquemático del filtro de la etapa de banda base 4                 |

| Figura 32 – Diagrama de Bode del filtro de banda base                                   |

| Figura 33 – Diagrama esquemático del filtro sobre la salida de los osciladores 42       |

| Figura 34 – Diagrama de Bode del filtro sobre la salida de los osciladores 44           |

| Figura 35 – Conversor DC-DC                                                             |

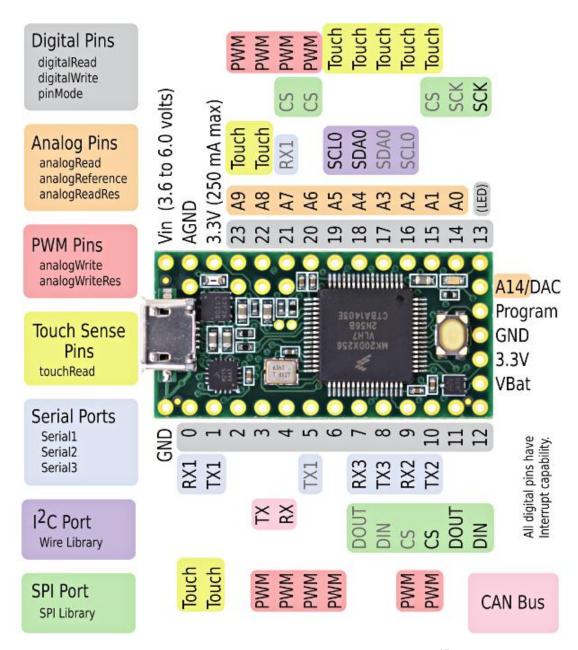

| FIgura 36 – Asignacion de pines de Teensy 3.2                                           |

| Figura 37 – Diagrama en bloques del código del microcontrolador                         |

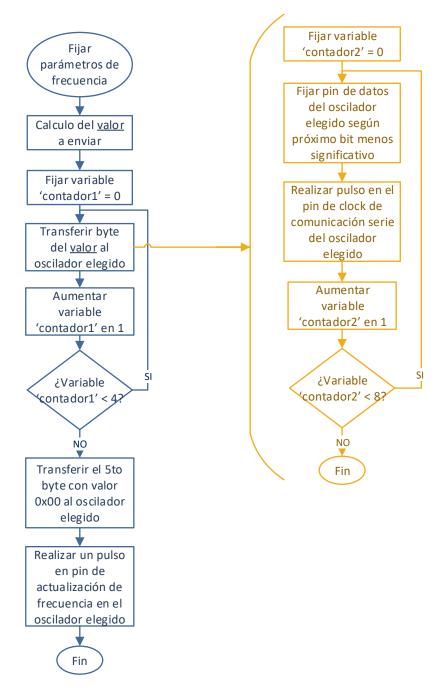

| Figura 38 – Diagrama de flujo de las funciones que programan los osciladores 5          |

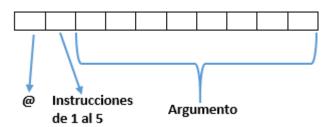

| Figura 39 - Formato de instrucciones que recibe el microcontrolador                     |

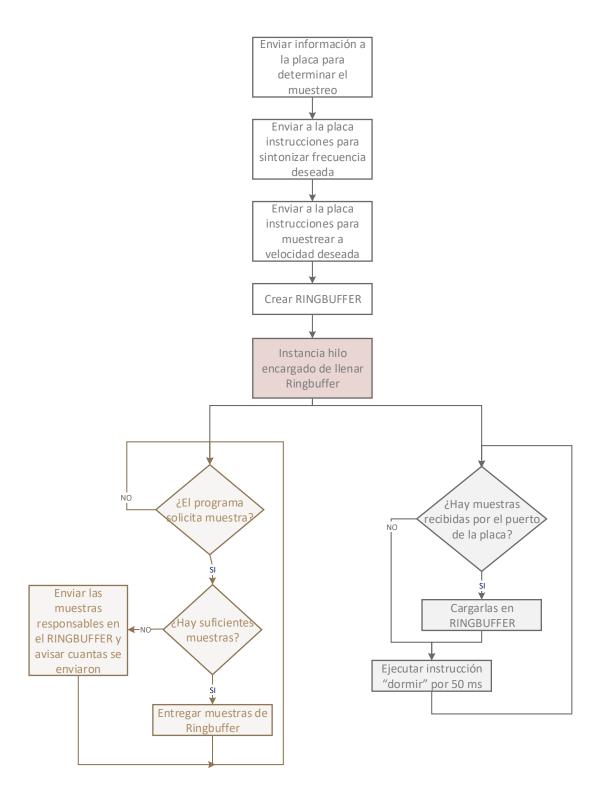

| Figura 40 – Diagrama de flujo del bloque de GNU Radio encargado de recibir muestra      |

| de la placa                                                                             |

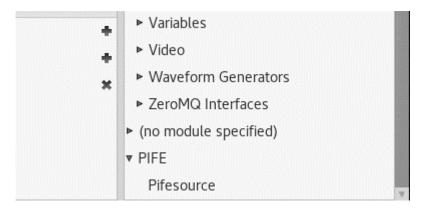

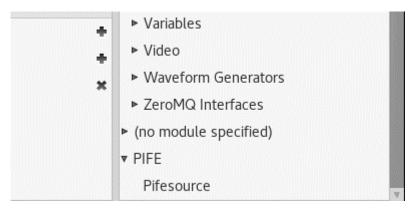

| Figura 41 – Módulo y bloque en la lista de GNU Radio Companion 56                       |

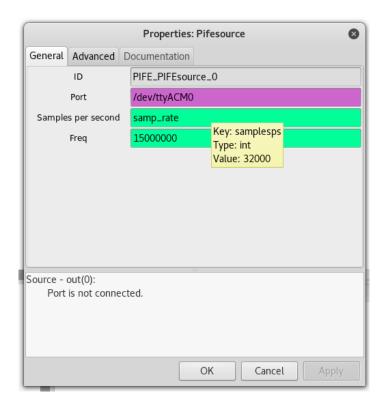

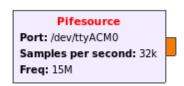

| Figura 42 – Bloque Pifesource dentro de GNU Radio Companion                             |

| Figura 43 – Configuración del bloque dentro de GNU Radio Companion                      |

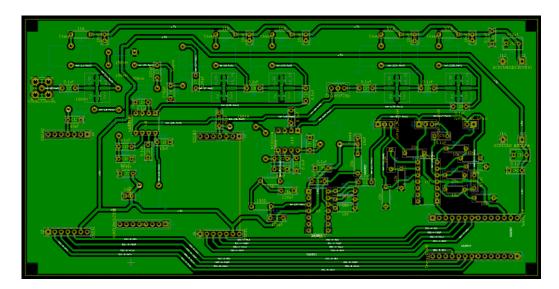

| Figura 44 – Diseño de PCB                                                               |

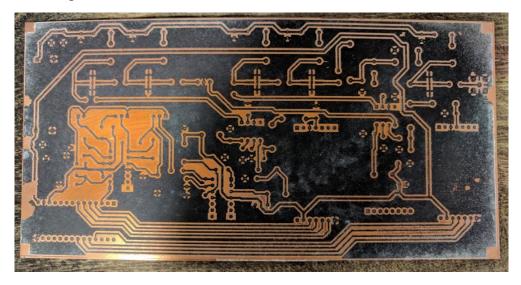

| Figura 45 – Tóner transferido a la placa                                                |

| Figura 46 – Placa de cobre sumergida en percloruro férrico a baño maría                 |

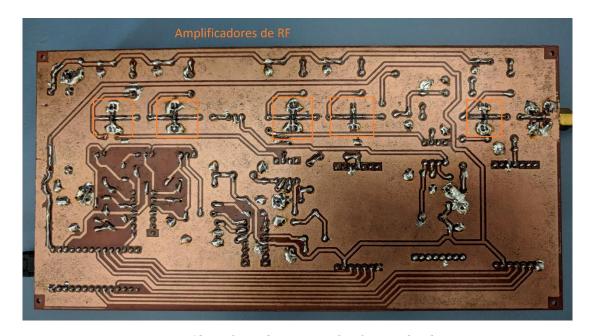

| Figura 47 – Placa de circuito final con nombre de componentes                           |

| Figura 48 – Placa de circuito final vista de abajo                                      |

| Figura 49 – Circuito para prueba de filtro de etapa de RF                               |

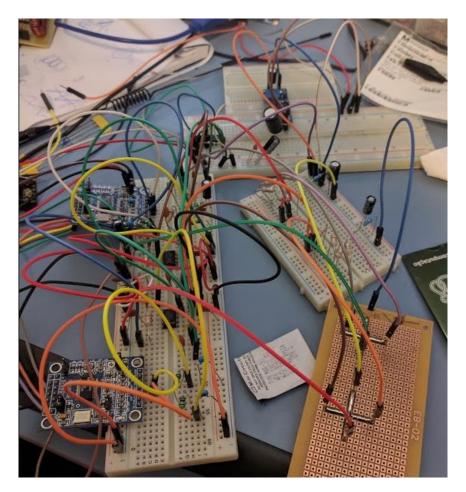

| Figura 50 – Prueba del circuito en protoboard                                           |

| Figura 51 – Amplificadores desconectados                                                |

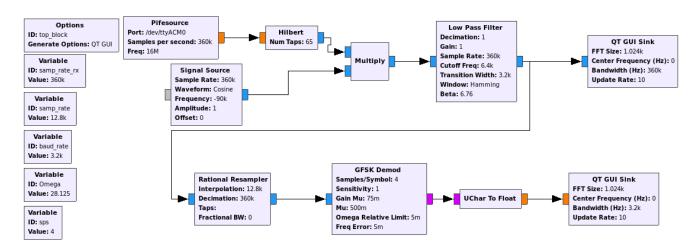

| Figura 52 – Diagrama de flujo en GNU Radio Companion para la transmisión en FM 64       |

| Figura 53 - Diagrama de flujo en GNU Radio Companion para la recepción de FM            |

| utilizando el bloque Pifesource                                                         |

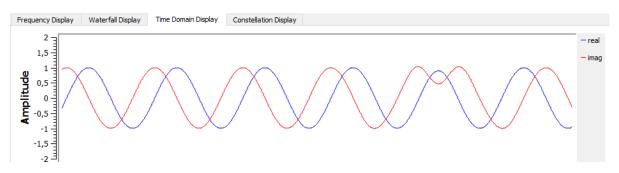

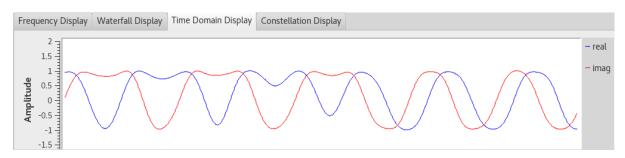

| Figura 54 – Gráfico en el dominio del tiempo de un fragmento de la señal FM transmitida  |

|------------------------------------------------------------------------------------------|

| 65                                                                                       |

| Figura 55 – Gráfico en el dominio del tiempo de un fragmento de la señal FM recibida     |

| (No es del mismo instante de la figura anterior)                                         |

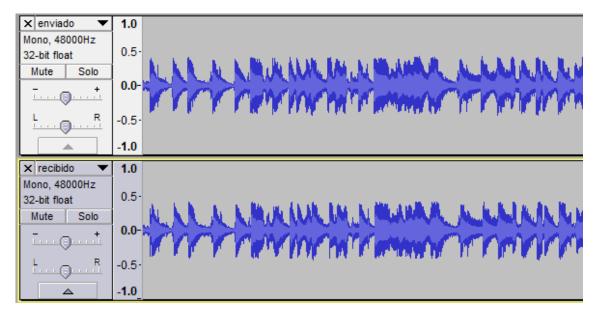

| Figura 56 - Formas de onda de música transmitida antes de ser modulada y enviada         |

| (arriba) y luego de ser recibida y demodulada (abajo)                                    |

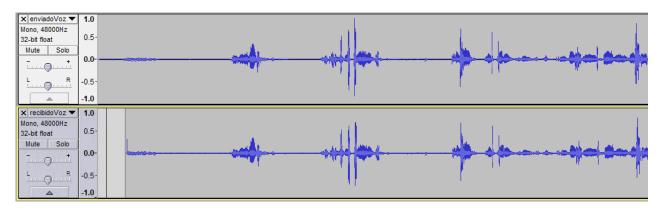

| Figura 57 - Formas de onda de audio con voz transmitido antes de ser modulado y enviado  |

| (arriba) y luego de ser recibido y demodulado (abajo)                                    |

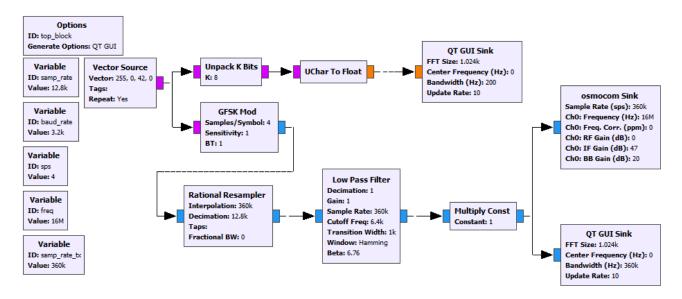

| Figura 58 - Diagrama de flujo en GNU Radio Companion para la transmisión de FSK          |

|                                                                                          |

| Figura 59 - Diagrama de flujo en GNU Radio Companion para la recepción de FSK            |

| utilizando el bloque Pifesource                                                          |

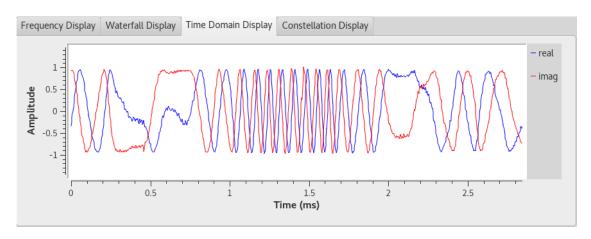

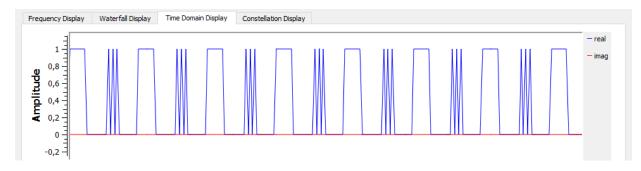

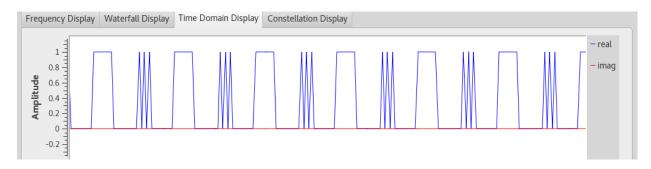

| Figura 60 – Gráfico en el dominio del tiempo de un fragmento de la señal FSK transmitida |

|                                                                                          |

| Figura 61 – Gráfico en el dominio del tiempo de un fragmento de la señal FSK recibida    |

| luego de un filtro pasa bajo (No es del mismo instante de la figura anterior) 69         |

| Figura 62 – Bits enviados [11111111,00000000,00101010,00000000] 69                       |

| Figura 63 – Bits recibidos [11111111,00000000,00101010,00000000] 69                      |

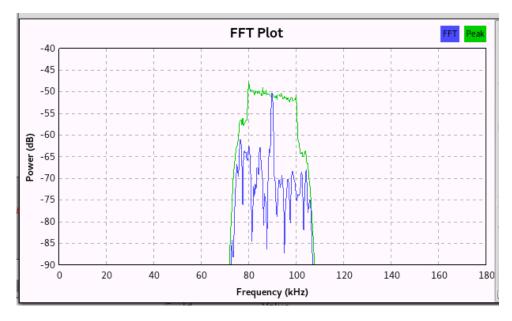

| Figura 64 – Configuración para prueba de sensibilidad                                    |

| Figura 65 – Recepción del barrido con -108dBm de entrada                                 |

| Figura 66 – Instalación de paquetes necesarios                                           |

| Figura 67 – Creación de módulo PIFE                                                      |

| Figura 68 – Creación de bloque PIFEsource                                                |

| Figura 69 – Compilación e instalación del módulo                                         |

| Figura 70 – Módulo y bloque instalados dentro de GNU Radio Companion                     |

| Figura 71 – Bloque PIFEsource en GNU Radio Companion                                     |

# Lista de Símbolos y Convenciones

#### Símbolos

Ω Ohm - Unidad de resistencia A Ampere – Unidad de Medida de corriente V Volts – Unidad de medida de tensión o voltaje Hertz – Unidad de frecuencia en ciclos por segundo Hz Samples per second / Muestras por segundo, unidad de medida de la sps, mps frecuencia de muestreo Prefijos 10<sup>-3</sup>, 10<sup>-6</sup>, 10<sup>-9</sup>, 10<sup>-12</sup> respectivamente m,u,n,pPrefijos 10<sup>3</sup>, 10<sup>6</sup>, 10<sup>9</sup> respectivamente k, M, G Factor de calidad o selectividad, mide relación entre energía reactiva que Q almacena y energía que disipa en un ciclo de señal, indica que tan aguda es la resonancia.

#### **Abreviaciones**

RF Radiofrecuencia/s

FI, IF Frecuencia intermedia

ADC Conversor analógico digital

SDR, RDS Radio definida por software

USB Universal Serial Bus

UART Universal Asynchronous Receiver-Transmitter

SPI Serial Peripheral Interface Bus

| I2C  | Inter-Integrated Circuit                                                                                                                                                          |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ISR  | Interrupt Service Routine                                                                                                                                                         |  |  |  |  |

| CDC  | Communications Device Class, clase de dispositivo USB que define su comportamiento.                                                                                               |  |  |  |  |

| DC   | Tensión Continua                                                                                                                                                                  |  |  |  |  |

| FIFO | First In, First Out, método para organizar elementos en una cola. El elemento más antiguo (primero que entro) es el primero en ser procesado.                                     |  |  |  |  |

| IIP3 | Punto de intercepción de 3er orden                                                                                                                                                |  |  |  |  |

| COM  | Puerto de comunicación                                                                                                                                                            |  |  |  |  |

| GBP  | Gain-Bandwidth Product, producto del ancho de banda y la ganancia de un amplificador.                                                                                             |  |  |  |  |

| DIP  | Dual in-line package, es una forma de empaquetado de circuito integrados que consiste en dos líneas paralelas de pines para insertar en un zócalo o de agujero pasante en un PCB. |  |  |  |  |

# **CAPÍTULO 1**

# Introducción

#### 1.1 Objetivos

#### 1.1.1 Objetivo General

El objetivo general del presente proyecto es el diseño y construcción de un prototipo receptor de señales de radiofrecuencia para la banda de HF. El equipo a desarrollar debe poder sintonizar canales dentro de dicha banda, digitalizarlos y transferirlos a una PC para su posterior procesamiento, siguiendo una metodología propia de un desarrollo profesional.

#### 1.1.2 Objetivos específicos

Como objetivos específicos del proyecto integrador se encuentran los siguientes:

- Integrar conocimientos adquiridos durante la carrera

- Obtener experiencia con el manejo de componentes de radiofrecuencia

- Familiarizarse con métodos de programación en el sistema operativo Linux

#### 1.2 Antecedentes

Dentro del Laboratorio de RF Y Microondas (LARFYM) donde se realiza el proyecto no existen antecedentes de proyectos integradores o tesinas de grado similares.

Dentro de la Facultad se encuentran algunos trabajos anteriores que realizan módulos específicos de radios definidas por software, generalmente focalizados en el procesamiento de las señales. En este trabajo, a diferencia de los anteriores, se focaliza en la plataforma para el acondicionamiento de la señal con el objetivo de ser digitalizada y el proceso de digitalización, sin realizar ningún desarrollo propio sobre el procesamiento de la información de la señal.

#### 1.3 Motivación

Como motivación personal del proyecto se incluye la persecución del título de grado, y específicamente para este proyecto es valorado por el autor la amplia cobertura de especialidades incluidas, ya que el trabajo incluye desarrollo de electrónica analógica de alta frecuencia, electrónica digital e informática.

Como motivación académica, dentro del LARFYM de la Facultad se deseaba trabajar con radios definidas por software (SDR) debido a su importante flexibilidad y su notable crecimiento como tecnología en comunicaciones a través de radiofrecuencias.

#### 1.4 Metodología para lograr los objetivos propuestos

El método utilizado en el proyecto consistió en modularizar el proyecto en etapas permitiendo trabajar en ellas de forma independiente. Esto dio la posibilidad de trabajar simultáneamente en estas etapas y en caso de demoras u obstáculos en algunas, poder continuar con las demás. También se pudieron realizar pruebas y prototipos en cada etapa para asegurarse su correcta respuesta previo a la conexión entre ellas para su funcionamiento global.

#### 1.5 Plan del proyecto

El proyecto consiste en el desarrollo de un receptor de radiofrecuencia que permita obtener la señal en la PC en tiempo real, siendo este de fácil configuración y que incluya un módulo para hacer de interfaz en el programa de software libre GNU Radio.

#### BANCHIO, Agustín Enrique

En las primeras etapas se realizó una investigación teórica sobre la arquitectura de los receptores de radio y las distintas tecnologías de los componentes. Luego se llevó a cabo un diseño de receptor que será sometido a prueba y corregido experimentalmente.

Se empleó un microcontrolador para que actúe como intermediario entre la PC y el receptor, se encargará de enviar las muestras a la PC y de recibir configuración de esta y aplicarla a los componentes del receptor.

Luego se realizó un módulo dentro del programa GNU Radio en PC para poder utilizar las muestras de la señal dentro de dicho programa.

En cada etapa se efectuaron pruebas para validar el diseño que se fue desarrollando y permitir encontrar soluciones y mejoras de manera temprana. En la última etapa se ejecutaron pruebas del sistema completo para obtener conclusiones en base a los objetivos propuestos.

# **CAPÍTULO 2**

# Radiocomunicaciones

El Capítulo 2 presenta un marco teórico general sobre el uso del espectro radioeléctrico, la forma de transportar información en ondas electromagnéticas y como se recibe en los receptores de radio.

#### 2.1 Radiocomunicación

Se define como radiocomunicación a toda transmisión, emisión o recepción de signos, señales, o información de cualquier naturaleza a través de ondas radioeléctricas.

Las ondas radioeléctricas son ondas electromagnéticas que se propagan por el espacio a la velocidad de la luz sin guía artificial fijadas por debajo de los 3000GHz

#### 2.2 Espectro Radioeléctrico

El Espectro Radioeléctrico es un recurso natural, de carácter limitado, que constituye un bien de dominio público, sobre el cual el Estado ejerce su soberanía. Es un medio intangible para servicios de comunicaciones. Se descompone en bandas de frecuencias que se atribuyen a distintos servicios y se asigna a usuarios autorizados para operarlas.

<sup>&</sup>lt;sup>1</sup> ENACOM: <a href="https://www.enacom.gob.ar/-que-es-el-espectro-radioelectrico-p117">https://www.enacom.gob.ar/-que-es-el-espectro-radioelectrico-p117</a> [Última visita: Noviembre 2017]

BANCHIO, Agustín Enrique

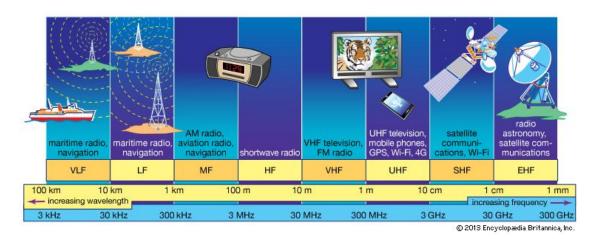

Figura 1 – Utilización comercial de bandas del espectro radioeléctrico<sup>2</sup>

La autoridad encargada de la atribución del espectro radioeléctrico en Argentina es el ENACOM (Ente Nacional de Comunicaciones), órgano que depende del Ministerio de Modernización. Para la toma de decisiones se tienen en cuenta las recomendaciones de la Unión Internacional de Telecomunicaciones (UIT o ITU en inglés).

Las resoluciones del ENACOM se reflejan en el Cuadro de Asignación de Bandas de la República Argentina.

La UIT subdivide el espectro radioeléctrico en nueve bandas como indica la siguiente tabla:

<sup>&</sup>lt;sup>2</sup> Imagen obtenida de: <a href="https://www.britannica.com/science/radio-frequency-spectrum">https://www.britannica.com/science/radio-frequency-spectrum</a> [Última Visita: Noviembre 2017]

BANCHIO, Agustín Enrique

Tabla 1 – Bandas de espectro radioeléctrico según UIT

| Número<br>de Banda<br>Según<br>UIT | Símbolos | Banda de<br>Frecuencias | Longitud de Onda       | Tipo de<br>Ondas |

|------------------------------------|----------|-------------------------|------------------------|------------------|

| 1                                  | ELF      | 3 a 30 Hz               | 100.000 a 10.000<br>Km |                  |

| 2                                  | SLF      | 30 a 300 Hz             | 10.000 a 1.000 Km      | Miriamétricas    |

| 3                                  | ULF      | 300 Hz a 3 KHz          | 1.000 a 100 Km         |                  |

| 4                                  | VLF      | 3 a 30 KHz              | 100 a 10 km            |                  |

| 5                                  | LF       | 30 a 300 KHz            | 10 km a 1 Km           | Kilométricas     |

| 6                                  | MF       | 300 a 3000 KHz          | 1.000 a 100 m          | Hectométricas    |

| 7                                  | HF       | 3 a 30 MHz              | 100 a 10 m             | Decamétricas     |

| 8                                  | VHF      | 30 a 300 MHz            | 10 a 1 m               | Métricas         |

| 9                                  | UHF      | 300 a 3000 MHz          | 100 a 10 cm            | Decimétricas     |

| 10                                 | SHF      | 3 a 30 GHz              | 10 a 1 cm              | Centimétricas    |

| 11                                 | EHF      | 30 a 300 GHz            | 10 a 1 mm              | Milimétricas     |

| 12                                 | THF      | 300 a 3000 GHz          | 1 a 0,1 mm             | Decimilimétricas |

#### 2.3 Modulación

En telecomunicaciones se denomina modulación al proceso de incluir la información a transmitir, sea digital o analógica, dentro de otra señal que puede ser físicamente transmitida.

La señal modulada, que se transmite, es el producto que resulta de modificar la señal portadora con la información de la señal modulante o moduladora.

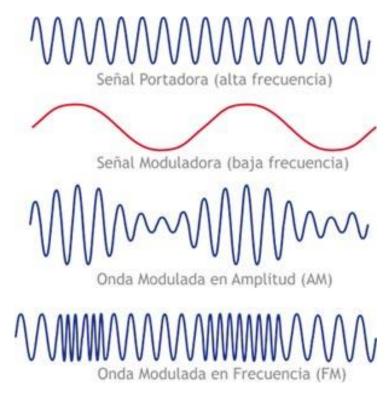

Figura 2 – Representación gráfica de las ondas moduladas en AM y FM, junto a las señales portadora y modulante.<sup>3</sup>

Se denomina modulador a aquellos dispositivos que permiten incorporar información sobre una señal portadora, siendo los demoduladores los que realizan el proceso inverso. Un modem es un dispositivo que puede realizar ambas operaciones.

Con la modulación se logra transportar la información que se desea transmitir a la frecuencia de la señal portadora. Esto permite la ubicar la señal en la banda deseada del espectro radioeléctrico, por ejemplo un canal de radio o un canal de televisión.

En modulación analógica, la modulación se aplica continuamente sobre la señal portadora en respuesta a la modulante. Las modulaciones analógicas más utilizadas son por amplitud (AM) o por frecuencia (FM).

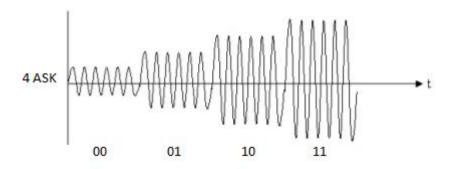

En modulación digital se utiliza un número finito de variaciones de fase, frecuencia o amplitud. Cada una de estas variantes representa un símbolo que se asigna a un patrón único de bits binarios. Si se utilizan  $M = 2^N$  símbolos, cada símbolo representa un patrón de N bits. Las modulaciones digitales más utilizadas son por niveles de amplitud (ASK), de frecuencia (FSK), de fase (PSK) o de amplitud y fase (QAM).

<sup>&</sup>lt;sup>3</sup> Imagen obtenida de: <a href="http://www.analfatecnicos.net/pregunta.php?id=15">http://www.analfatecnicos.net/pregunta.php?id=15</a> [Última visita: Octubre 2017]

Figura 3 – 4 Símbolos de modulación ASK

#### 2.4 Receptor de Radio

Un receptor de radio es un dispositivo o circuito electrónico capaz de extraer información utilizable de las ondas electromagnéticas que recibe.

El diseño de receptor más utilizado es el del receptor superheterodino.

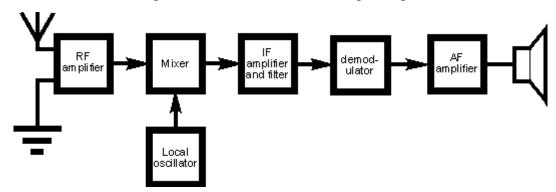

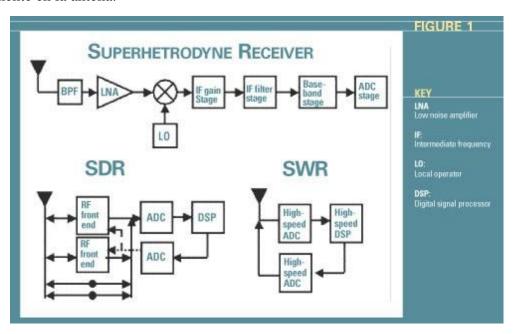

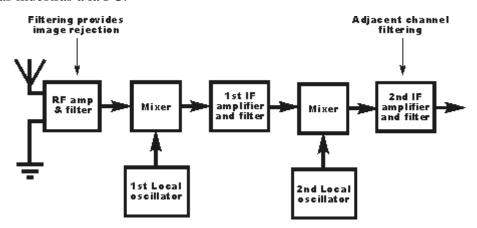

Figura 4 – Diagrama de bloques de receptor superheterodino<sup>4</sup>

En este tipo de receptores, la señal de radiofrecuencia es desplazada a una frecuencia intermedia (IF) a través de un mezclador antes de ser procesada por filtros específicamente seleccionados para esta IF con alta selectividad y finalmente demodulada con algún componente demodulador, si la información es audio, la última etapa consiste en un amplificador de audio y una salida por parlante.

<sup>&</sup>lt;sup>4</sup> Imagen obtenida de: <a href="http://www.radio-electronics.com/info/rf-technology-design/superheterodyne-radio-">http://www.radio-electronics.com/info/rf-technology-design/superheterodyne-radio-</a> receiver/block-diagram.php [Última visita: Octubre 2017]

BANCHIO, Agustín Enrique

Algunos receptores, llamados de doble conversión, utilizan dos frecuencias intermedias para mayor rechazo de frecuencia imagen y para obtener mayor selectividad. Al utilizar dos frecuencias intermedias requieren de dos mezcladores.

En caso de ser un receptor de radio definida por software, luego del mezclador se coloca un conversor analógico digital que muestrea la señal para luego poder ser procesada por algoritmos de software.

Otra arquitectura de receptores utilizados en radios definidas por software no utiliza mezclador y en cambio ubica el conversor analógico digital luego de una sola etapa de amplificación y filtrado. Al muestrear las señales en su frecuencia de origen sin pasar por un mezclador se necesitan más muestras por segundo, esto a su vez permite tener un ancho de banda más grande. Esta arquitectura precisa de conversores analógicos digitales de velocidades mucho más altas (incluso llegando a varias Gsps) y se aproxima más a una radio definida por software ideal, que utilizaría un conversor analógico digital conectado directamente en la antena.

Figura 5 – Diagramas de bloques de distintos receptores de radios definidas por software<sup>5</sup>

<sup>&</sup>lt;sup>5</sup> Imagen obtenida de: <a href="http://urgentcomm.com/mag/uwb-brings-radios-future-closer">http://urgentcomm.com/mag/uwb-brings-radios-future-closer</a> [Última visita: Noviembre 2017]

### Componentes de un receptor de radio

#### 2.4.1 Antena

La antena es el componente que convierte potencia eléctrica en ondas de radio en caso de transmisión, y viceversa para el caso de recepción. Típicamente están construidas con materiales conductores. Los campos eléctricos y magnéticos oscilantes de una onda entrante ejercen una fuerza sobre los electrones de estos conductores, produciendo corrientes oscilantes a lo largo de la antena.

Las antenas pueden ser diseñadas para transmitir o recibir ondas en todas las direcciones horizontales (omnidireccionales) o en alguna dirección en particular (direccional). Por lo general la amplitud de la señal recibida por la antena es demasiado baja (del orden de microvoltios de pico a pico) para ser demodulada directamente y requiere ser amplificada para su utilización.

### 2.4.2 Amplificador de radiofrecuencia

Un amplificador es un dispositivo electrónico capaz de utilizar energía de una fuente para incrementar la amplitud de una señal. Un amplificador de radiofrecuencia tiene que ser capaz de amplificar señales de frecuencias superiores a las de un amplificador de señales de audio o un controlador para un motor. Además se caracteriza por introducir bajo nivel de ruido.

Un amplificador puede ser una válvula, un transistor, o parte de un circuito integrado con más elementos. Es común en amplificadores de radiofrecuencia que su entrada y salida estén adaptados en impedancia para maximizar la transferencia de energía.

#### 2.4.2.1 Parámetros de un amplificador de radiofrecuencia

- Ganancia: Es la medida de la capacidad de incrementar la potencia o amplitud de una señal de la entrada a la salida. Por lo que un amplificador tiene que tener una ganancia superior a 1. La ganancia también puede ser expresada en dB.

- **Frecuencia de trabajo**: Es el rango de frecuencias en el cual el amplificador tiene una respuesta con ganancia superior a la unidad.

- Figura de ruido: La figura de ruido es una medida de degradación de la relación señal-ruido causada por componentes en la cadena de la señal de radiofrecuencia.

Es la relación entre el ruido en la salida del componente y el ruido que quedaría si éste no hubiera introducido ninguno. Se mide en decibeles, y a valores más chicos mejor desempeño.

- Estabilidad: En la práctica, existen caminos de señal desde la salida del amplificador (donde la potencia es mayor debido a la ganancia) hacia la entrada. Es posible que para ciertos valores de carga, el coeficiente de reflexión de entrada exceda la unidad, transformando el circuito en un amplificador de reflexión en la entrada. Algunos valores de coeficiente de reflexión de fuente a la entrada pueden provocar que el coeficiente de reflexión de salida supere la unidad. Si alguno de estos casos o ambos suceden, se dice que el circuito es condicionalmente estable, o potencialmente inestable. Un amplificador es incondicionalmente estable si es estable para todas las frecuencias para la cual su ganancia es mayor a la unidad, y para cualquier impedancia de carga y fuente.

### 2.4.3 Mezclador

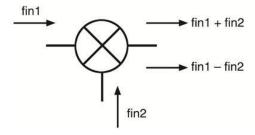

El mezclador es un dispositivo de 3 puertos, activo o pasivo, que puede modular o demodular una señal. Se utiliza para cambiar la frecuencia de una señal mientras se preservan el resto de sus características como fase y amplitud.

La señal de radio frecuencia entra por un puerto, y una señal provista por un oscilador local entra por otro, y por el puerto de salida se obtienen la suma y la diferencia en frecuencia de las entradas.

Figura 6 – Representación simbólica de un mezclador<sup>6</sup>

Página 12

<sup>&</sup>lt;sup>6</sup> Imagen obtenida de: <a href="https://www.digikey.com/en/articles/techzone/2011/oct/the-basics-of-mixers">https://www.digikey.com/en/articles/techzone/2011/oct/the-basics-of-mixers</a>

[Última visita: Octubre 2017]

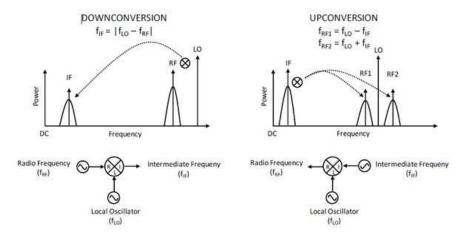

Cuando la frecuencia deseada es menor a la frecuencia de entrada, el proceso se llama conversión descendente. Cuando la frecuencia deseada es mayor, el proceso se llama conversión ascendente.

El mezclador se utiliza en un receptor para desplazar la señal de radiofrecuencia a una de frecuencia intermedia. Los mezcladores activos son configurados para obtener ganancia de conversión, aislación entre puertos y requerir menos potencia del puerto de oscilador local.

Figura 7 – Representación de conversión descendente y conversión ascendente<sup>7</sup>

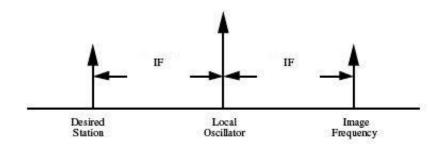

### 2.4.3.1 Frecuencia Imagen

Debido a que en la salida, se encuentran la suma y la diferencia de las entradas, para una frecuencia específica de oscilador local, dos frecuencias de entrada producirán la misma frecuencia intermedia, la frecuencia con la señal deseada y una frecuencia imagen. Para impedir que esto suceda en la entrada del amplificador se debe colocar un filtro para el rango de trabajo del receptor, que filtre todas las frecuencias imagen, así a la salida del mezclador solo está presente la señal deseada.

\_

<sup>&</sup>lt;sup>7</sup> Imagen obtenida de: <a href="https://www.digikey.com/en/articles/techzone/2011/oct/the-basics-of-mixers">https://www.digikey.com/en/articles/techzone/2011/oct/the-basics-of-mixers</a>

[Última visita: Octubre 2017]

Figura 8 – Representación en frecuencia de frecuencia imagen respecto a frecuencia del oscilador y de la señal deseada<sup>8</sup>

#### 2.4.3.2 Parámetros de un mezclador

- Pérdida o ganancia de conversión: Se mide en decibeles y es la ganancia que recibe la señal en un mezclador activo o la pérdida que sufre en un mezclador pasivo.

- Punto de intercepción de 3er orden (IIP3): Es el nivel de potencia de la señal de entrada que produce a la salida el mismo nivel de señal deseada que de productos de intermodulación no deseados.

- Aislación de puertos: Indica la potencia que se fuga de un puerto a otro. Para no

obtener interferencia de la señal de RF y el oscilador local a la salida, se deberá

utilizar alta aislación.

- **Figura de ruido**: Al igual que en un amplificador, un mezclador inserta una cantidad de ruido a la salida y determina el valor de figura de ruido.

- Punto de 1dB de compresión: Si se aumenta el valor de potencia de RF a la entrada, también aumenta el valor de FI a la salida con la ganancia o pérdida de conversión. Pero si la potencia de RF es demasiado grande el mezclador se saturará (compresión) y la potencia de FI en la salida no aumentará en la misma proporción. Los fabricantes de mezcladores especifican la potencia de entrada de RF que produce 1dB de compresión en la señal.

\_

<sup>&</sup>lt;sup>8</sup> Imagen obtenida de: <a href="https://www.quora.com/What-is-the-image-frequency">https://www.quora.com/What-is-the-image-frequency</a> [Última visita: Octubre 2017]

#### 2.4.4 Oscilador Local

Un oscilador local es un oscilador electrónico que se usa en conjunto con mezcladores. Producen una onda senoidal o cuadrada que es utilizada para cambiar la frecuencia de la señal en un receptor superheterodino. Un requerimiento de los osciladores es que no emitan armónicos ni espurias que puedan interferir en el proceso de conversión.

### 2.4.4.1 Tipos de osciladores locales

- Oscilador de cristal: Utilizando la resonancia de un cristal piezoeléctrico se consigue alta estabilidad por bajo costo, pero a una frecuencia fija. Para cambiar frecuencias se debe cambiar el cristal.

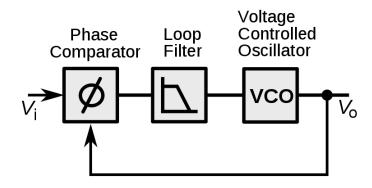

- Lazo de fase enganchado (PLL): Utiliza un oscilador controlado por voltaje (VCO) y un sistema de control que relaciona la fase de la señal a la salida con la señal a la entrada para mantener las fases emparejadas. Utilizando divisores de frecuencia dentro del lazo de control se pueden obtener a la salida múltiplos de la frecuencia a la entrada. Y variando estos divisores se obtiene un oscilador de frecuencia variable. Si bien estos osciladores llegan a muy altas frecuencias (GHz), al estar presente un lazo de control estos osciladores tienen limitaciones de estabilidad y velocidad para fijar una frecuencia.

Figura 9 – Diagrama de bloques de un oscilador PLL.<sup>9</sup>

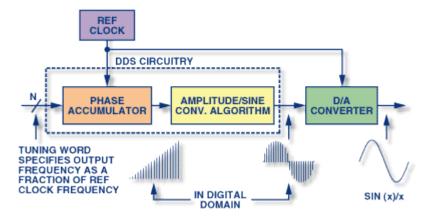

• Síntesis digital directa (DDS): Permite crear ondas de forma arbitraria a partir de un clock de frecuencia fija. Contiene almacenados en memoria suficientes puntos

<sup>&</sup>lt;sup>9</sup> Imagen obtenida de: <a href="https://en.wikipedia.org/wiki/Phase-locked loop">https://en.wikipedia.org/wiki/Phase-locked loop</a> [Última visita: Octubre 2017]

de la función a sintetizar en forma digital. Estos valores digitales son alimentados a un conversor digital analógico a rápida velocidad obteniendo como resultado la onda con la frecuencia deseada con altísima precisión (del orden de miliHertz). Presenta más agilidad para cambiar de frecuencia respecto a un PLL (millones de veces por segundo), no tiene problemas de inestabilidad de lazo de control, pero es costoso para muy altas frecuencias (mayor a 100MHz).

Figura 10 – Diagrama de bloques de oscilador de síntesis digital directa. 10

### 2.4.5 Filtros

Los filtros electrónicos son circuitos que realizan procesamiento de señales, en especial para disminuir componentes de frecuencia no deseados, amplificar frecuencias deseadas o ambos.

#### 2.4.5.1 Tipos de filtros según su tecnología

- **Pasivos**: Son filtros de combinaciones de Resistencias, Capacitores e Inductores, no dependen de una fuente de alimentación externa.

- **Activos**: Son filtros que además de componentes pasivos incluyen componentes activos, frecuentemente amplificadores operacionales.

- Filtro de cristal: Son circuitos que aprovechan la característica piezoeléctrica de los cristales cuarzo. Estos cristales presentan resonancias mecánicas de entre 10.000 a 100.000 veces de factor Q, mucho mayores a los creados con inductores

Página 16

<sup>&</sup>lt;sup>10</sup> Imagen obtenida de: <a href="http://www.analog.com/en/analog-dialogue/articles/all-about-direct-digital-synthesis.html">http://www.analog.com/en/analog-dialogue/articles/all-about-direct-digital-synthesis.html</a> [Última visita: Octubre 2017]

y capacitores. La estabilidad y alto factor Q del cristal permite frecuencias precisas y alta selectividad.

Filtro cerámico: Similar al filtro de cristal pero utilizando resonadores cerámicos, que también tienen características piezoeléctricas. Son más baratos pero presentan menos selectividad.

#### 2.4.5.2 Tipos de filtros según su respuesta en frecuencia

Una frecuencia se considera rechazada cuando su atenuación específica supera los 3dB. La frecuencia a la que se la atenúa exactamente 3dB se la llama frecuencia de corte.

- Filtro pasa bajo: Filtro que atenúa las frecuencias superiores a una frecuencia de corte.

- **Filtro pasa alto**: Filtro que atenúa las frecuencias inferiores a una frecuencia de corte.

- **Filtro pasa banda**: Filtro que atenúa frecuencias que se encuentren fuera de un rango o banda.

- Filtro rechaza banda: Filtro que atenúa frecuencias dentro de un rango o banda.

También existen filtros de usos muy específicos como filtros peine que presentan varias bandas de paso separadas regularmente, o filtros en los que todas las frecuencias pasan y solo la fase es modificada.

### 2.4.5.3 Rechazo de frecuencia imagen

Para que no se mezcle la señal deseada con la señal imagen no deseada en el mezclador, se suele seleccionar una FI mayor a la mitad del ancho del rango de trabajo deseado y luego se utiliza un filtro pasa banda que filtre frecuencias fuera de ese rango, de forma que sintonizando cualquier frecuencia del rango de trabajo, la frecuencia imagen quede atenuada por el filtro.

Otra solución es usar distintos filtros y conmutarlos según cual se necesite. De esta forma se puede obtener un rango de trabajo mucho mayor y la FI no tiene que ser mayor a la mitad del ancho.

### 2.4.6 Demodulador

Un demodulador es un circuito electrónico que se encarga de recuperar la información contenida en la señal. Hay varios métodos de modulación, por lo que hay varios tipos de demoduladores. La salida de estos dispositivos puede ser sonido (si se busca recuperar una señal de audio), imágenes (como en una señal de TV), datos binarios (en una señal digital), etc.

De acuerdo a la técnica de modulación será el modulador que se debe utilizar. Si un receptor de radio debe recuperar información de varias técnicas de modulación deberá tener incluido un circuito específico para cada técnica a demodular.

### 2.4.6.1 Ejemplos de técnicas de demodulación

La modulación analógica por amplitud puede ser demodulada por un detector de envolvente, que puede ser un simple diodo rectificador. Otro método puede estar basado en el uso de un mezclador, recuperando la banda base.

La modulación analógica por frecuencia puede ser demodulada con un detector de cuadratura que multiplica la señal consigo misma desfasada 90 grados, obteniendo como uno de los términos resultantes la información original que puede ser filtrada. Otro método es alimentar un PLL con la señal, obteniendo la información como la señal de error del lazo de control.

## 2.5 Radio definida por software

Una radio definida por software (SDR) es un sistema de radiocomunicación donde algunos componentes que normalmente se implementan en hardware, como mezcladores, filtros, demoduladores, amplificadores, etc.) son realizados a través de software por medio de una PC o un sistema embebido.

Las etapas por las que pasa la señal dentro de un receptor o transmisor, pueden describirse matemáticamente, es decir cada componente tiene una respuesta conocida matemáticamente. Esto implica que si la señal se encontrara muestreada de forma digital y se le aplicaran funciones matemáticas con un procesador a esta señal digitalizada, se podrían obtener los mismos resultados que la señal obtendría si pasara por componentes reales que la modifiquen.

### DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR

### BANCHIO, Agustín Enrique

Una radio definida por software utiliza un conversor analógico digital para muestrear la señal y una vez que ésta se encuentra en forma digital se le aplican operaciones matemáticas en remplazo de los componentes que realizan la misma función de manera analógica.

Aunque se limite la resolución de la señal a aquella del conversor analógico digital, se pueden implementar operaciones que no son posibles de realizar por hardware o que serían muy costosas e imprecisas. Además el hecho de que se realicen por software brinda un dinamismo muy superior al receptor completamente en hardware. Para cambiar un parámetro del receptor solo se necesita cambiar el software y no algún componente de hardware.

### 2.5.1 Conversor analógico digital

Un conversor analógico digital (ADC) es un circuito electrónico que convierte una señal analógica en una señal digital. Convierte un voltaje o corriente de entrada a un número proporcional a su magnitud expresado digitalmente. Un conversor digital analógico (DAC) realiza la función inversa.

#### 2.5.1.1 Arquitecturas de conversores analógicos digitales

Existen varias arquitecturas de hardware para implementar un conversor analógico digital. Las 2 más utilizadas son:

- Por aproximaciones sucesivas: Utiliza un comparador para comparar el voltaje de entrada con la salida de un conversor digital analógico interno que va aproximándose sucesivamente al valor correcto. En cada paso se obtiene un bit de conversión y el rango de comparación se reduce a la mitad.

- Conversión directa o Flash: Utiliza varios comparadores en paralelo, cada uno comparando con escaleras de voltajes construidas generalmente con varios resistores. La salida es luego codificada en binario por un encoder. Como no requieren acercarse al resultado en una serie de etapas son extremadamente rápidos, pero al requerir 2<sup>n</sup>-1 comparadores para una conversión de n bits se tornan más costosos mientras aumenta la precisión.

### DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR

BANCHIO, Agustín Enrique

#### 2.5.1.2 Parámetros de un conversor analógico digital

Un conversor analógico digital convierte una señal analógica continua en el tiempo y en amplitud en una señal digital discreta en el tiempo y amplitud. El conversor puede trabajar solo hasta cierta velocidad. Esto implica que aparecerán errores, ruidos y limitaciones. Ciertos parámetros caracterizan a los conversores analógicos digitales para saber si se pueden utilizar en una aplicación específica. Entre los más importantes se destacan:

- Resolución: Indica la cantidad de valores posibles que puede tener la señal discretizada. Una resolución de 8 bits significa que los infinitos valores de amplitud de la señal se discretizarán en 256 distintos valores según su proximidad. Esto introduce un error de cuantificación por el redondeo de la entrada analógica a la salida digital, que es menor mientras mayor resolución tenga el conversor. Para aprovechar toda la resolución del conversor se debe amplificar la señal a convertir para que se utilice todo el rango de conversión.

- Velocidad de muestreo: Es el ritmo en el que la señal es muestreada. Si las

muestras se toman cada un cierto tiempo conocido, la señal original puede ser

reconstruida a partir de valores discretos de tiempo utilizando fórmulas de

interpolación. Esto sólo se logra si la velocidad de muestreo es mayor al doble de

la frecuencia máxima presente en la señal, según el teorema de Nyquist-Shannon.

# CAPÍTULO 3

# Microcontroladores y comunicación con PC

El capítulo 3 brinda un pequeño marco teórico sobre el uso de microcontroladores para configurar los componentes del receptor y establecer comunicación con la PC.

### 3.1 Microcontrolador

Un microcontrolador es un circuito integrado que contiene al menos un procesador (CPU), memoria y periféricos de entrada y salida programables. Se incluye memoria RAM y memoria de programa EEPROM o flash. Los microcontroladores están diseñados para sistemas embebidos. Su principal fuerte es reducir el tamaño y costo en comparación a diseños que utilizan procesador, memoria y dispositivos de entrada y salida separados. Usualmente los microcontroladores también contienen otros periféricos como conversores analógico digitales (ADC) y conversores digital analógicos (DAC), bloques de PWM, etc.

Los microcontroladores modernos permiten desarrollar prototipos de forma rápida y económica, con interfaces de programación simples y precios cada vez más bajos.

### 3.1.1 Periféricos y Entradas/Salidas

Los microcontroladores presentan pines que pueden ser utilizados como entrada o como salidas y estos permiten interactuar con otros componentes, pantallas, LEDs, sensores, etc.

Además los microcontroladores pueden incluir circuitos especiales para utilizar protocolos de comunicación a través de ciertos pines sin la necesidad de emular el protocolo a través de software (bit banging). Los protocolos de comunicación más comunes son UART, USB, SPI, I2C y Ethernet. Utilizando hardware dedicado se elimina cierta carga sobre el procesador.

### 3.1.2 Interrupciones

Las interrupciones le permiten a un sistema responder en tiempo real cuando ciertos eventos ocurren.

El sistema de interrupciones le señaliza al procesador que suspenda el procesamiento de la instrucción actual y que comience una rutina para "atender" la interrupción (ISR). Esta rutina incluye cualquier procesamiento necesario dependiendo de la interrupción.

Las interrupciones se utilizan para atender de manera rápida a los eventos que necesitan ese nivel de repuesta. En los sistemas de interrupciones avanzados, las interrupciones tienen un número de prioridad que indica qué interrupciones pueden interrumpir a otras, en caso que alguna interrupción interrumpa a otra mientras se la está atendiendo.

Los eventos que pueden causar interrupciones pueden ser externos como el cambio en un pin de entrada o internos como timers, estos últimos son muy utilizados para medir tiempo.

### 3.2 Comunicación USB

USB es un estándar que define cables, conectores y protocolos de comunicaciones para conectar, comunicar y alimentar computadoras y dispositivos. Fue diseñado para estandarizar la conexión de periféricos de computadora a computadoras personales, tanto para alimentar como para comunicar dichos dispositivos.

En cuanto a especificaciones de potencia todos los puertos USB trabajan a 5V, en el estándar USB 2.0 se permite un máximo de 500mA por puerto, mientras que en USB 3.0 este aumenta a 900mA, y en caso de utilizar solo alimentación el valor de corriente puede superar los 3A y el valor de tensión también puede aumentar a más de 20V.

### DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR

BANCHIO, Agustín Enrique

En cuanto a especificaciones de velocidad de transferencia, en USB 1.0 se definieron ratios de 1.5Mbit/s (Low Speed) y 12Mbit/s (Full Speed). En USB 2.0 se definió 480Mbit/s (High Speed) y en USB 3.0 se definió 5Gbit/s (SuperSpeed).

### 3.2.1 Protocolo de comunicación

La arquitectura de comunicación USB es asimétrica, consistiendo en un host y multiples dispositivos (devices). No se puede realizar comunicación entre dos host sin adaptadores que creen dispositivos en el medio. Algunos microcontroladores incluyen puertos que pueden hacer de host o device, pero en su mayoría estos sólo pueden actuar de device.

Las transferencias de datos son dirigidas por el host, quien realiza un polling<sup>11</sup> en los dispositivos conectados para revisar si quieren realizar una transferencia.

Las transferencias de datos pueden ser de los siguientes tipos:

- Transferencias isócronas: Garantizan ancho de banda específico.

- Transferencia interrupt: Para dispositivos que necesitan respuestas rápidas garantizadas (Como teclados o ratones.)

- Transferencias bulk: Transferencias grandes esporádicas utilizando todo el ancho de banda disponible, no garantiza latencia ni ancho de banda específicos.

La funcionalidad de un dispositivo USB puede ser definida por su código de clase que envía al host. Por lo general los dispositivos de Communications Device Class (CDC) pueden ser interpretados por la PC como puertos series COM virtuales.

Por lo general el protocolo de comunicación es simplificado mediante abstracción por hardware dedicado y bibliotecas.

### 3.3 Ringbuffers

Un ringbuffer o buffer circular es una estructura de datos que utiliza un buffer de tamaño fijo como si sus extremos estuvieran conectados. Utiliza un puntero de escritura que introduce los elementos y un puntero de lectura para leerlos, eliminando la necesidad

<sup>&</sup>lt;sup>11</sup> Polling es el proceso por el cual una computadora o dispositivo espera a que un dispositivo externo verifique si se encuentra en determinado estado.

### DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR

BANCHIO, Agustín Enrique

de desplazar todos los elementos cuando uno es leído. Por su funcionamiento el ringbuffer es un buffer adecuado para utilizar como FIFO.

Figura 11 – Ringbuffer con los punteros de lectura y escritura

# **CAPÍTULO 4**

## Desarrollo del proyecto

El Capítulo 4 brinda un marco metodológico del desarrollo del prototipo.

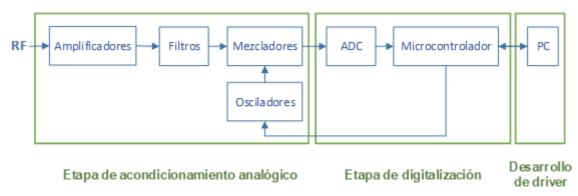

### 4.1 Descripción general del proyecto

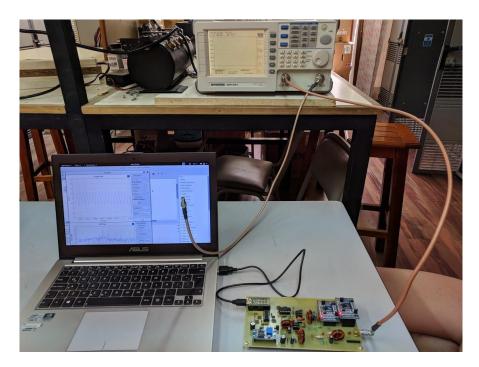

El objetivo principal de este trabajo es diseñar y construir un prototipo que sintonice, acondicione señales de RF para su digitalización, las digitalice y luego envíe la señal muestreada por USB a la PC. El proyecto consta de tres partes, la primera es la parte analógica de acondicionamiento de la señal de radiofrecuencia, la segunda es la de digitalización y comunicación con la PC y la tercera es el desarrollo de un driver que permita utilizar el dispositivo con el software de la PC.

El prototipo deberá entregar a la PC las muestras de la señal sintonizada en la frecuencia deseada dentro del rango de trabajo.

Debido a que el microcontrolador se conectará a la PC mediante USB, se aprovechará esa conexión para alimentar todos los componentes. Según las especificaciones USB 1.0 y 2.0, un puerto es capaz de entregar hasta 500mA en la línea de 5V. Por lo que, como criterio de diseño del dispositivo se incluye que su consumo se encuentre por debajo de ese límite.

Otro criterio a tener en cuenta en el diseño es que el sistema sea de fácil testeo, lo que implica que se pueda probar el comportamiento de los distintos componentes, cambiarlos en caso de mal funcionamiento y medir distintos valores de tensión y corriente en varias partes del circuito durante la fase de desarrollo. Para esto se busca que los

componentes sean compatibles con protoboard, de fácil soldado y en lo posible de encapsulado de agujero pasante.

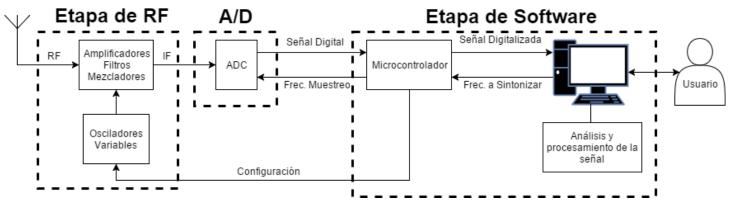

### 4.1.1 Diagrama de Bloques General

A continuación se muestra el diagrama de bloques general del proyecto:

Figura 12- Diagrama de bloques del proyecto

El desarrollo del prototipo se divide en 3 etapas, el acondicionamiento analógico, la digitalización y el driver de PC.

El desarrollo del acondicionamiento analógico comprende:

- Elección de la arquitectura del receptor

- Diseño e implementación de filtros

- Elección de amplificadores, mezcladores y osciladores

El desarrollo de la etapa de digitalización comprende:

- Programación del microcontrolador para que:

- o Reciba la configuración deseada por USB

- o Muestree la señal con su conversor analógico-digital.

- o Configure los osciladores a las frecuencias necesarias.

- Envíe las muestras por USB

El desarrollo del driver en la PC comprende:

- Desarrollo de un módulo para el software libre GNU Radio en el sistema operativo

Linux que :

- o Envíe la configuración deseada al dispositivo

- o Reciba las muestras y las inserte en el flujo de muestras de GNU Radio

### 4.2 Acondicionamiento analógico

A continuación se desarrollan las etapas que conforman el front end de radiofrecuencia encargado de sintonizar y acondicionar la señal para su digitalización.

### 4.2.1 Arquitectura del receptor

Se optó por diseñar un receptor superheterodino de doble conversión, con una conversión llevando la señal sintonizada a una frecuencia intermedia para simplificar su filtrado y selectividad, y otra para llevar la señal a banda base donde será digitalizada.

Se prefirió esta arquitectura por sobre la arquitectura que no realiza mezcla, ya que esta última resulta mucho más costosa en cuanto al ADC y además requiere de una velocidad de transferencia muy grande, y por lo tanto también costosa, para transferir todas las muestras a la PC.

Figura 13 – Receptor superheterodino de doble conversión. 12

La razón de la doble conversión es la mayor selectividad del canal al utilizar una conversión extra, y al poder utilizar una frecuencia intermedia mayor se aleja la frecuencia imagen que se debe filtrar, la segunda FI es más baja, y permite una etapa de digitalización más simple.

Esta arquitectura precisa de dos osciladores locales, uno de los cuales debe ser variable para poder sintonizar la señal que se quiere recibir, mientras que el otro no

<sup>&</sup>lt;sup>12</sup> Imagen obtenida de: <a href="http://www.radio-electronics.com/info/rf-technology-design/superheterodyne-radio-receiver/double-superheterodyne-receiver.php">http://www.radio-electronics.com/info/rf-technology-design/superheterodyne-radio-receiver/double-superheterodyne-receiver.php</a> [Última visita: Octubre 2017]

requiere ser variable, ya que la diferencia entre la frecuencia intermedia y la banda base es siempre la misma. También requiere de dos mezcladores.

### 4.2.2 Osciladores

Ya que la frecuencia a sintonizar debe ser definida digitalmente, los osciladores deben poder variarse a través de una interfaz digital. Entre las distintas opciones, debido a que el DDS no posee los problemas de inestabilidad de un PLL, es un sistema íntegramente digital y posee rapidez para cambiar de frecuencia, se lo consideró superior para esta aplicación ya que las frecuencias utilizadas en este proyecto se encuentran dentro de los rangos en los que comúnmente trabaja este tipo de oscilador.

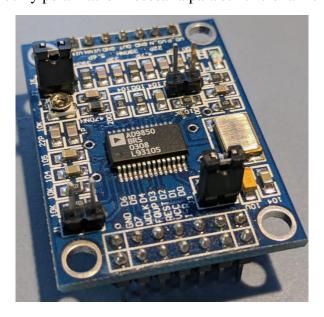

Los osciladores seleccionados son dos sintetizadores digitales de ondas senoidales AD9850 de Analog Devices. Cada uno ofrece rango dinámico libre de espurias mayor a 50dB en salidas de 40MHz, puede ser programado con una precisión de 0,0291 Hz y permite hasta 23 millones de cambios de frecuencia por segundo. Llegan hasta 50MHz y la configuración puede ser cargada serialmente o en paralelo. Para utilizar la menor cantidad de líneas del microcontrolador, es preferible utilizar el modo serial.

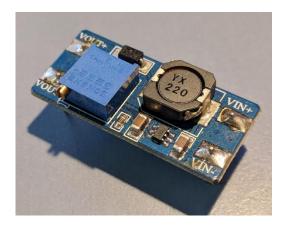

El sintetizador AD9850 fue seleccionado junto a su placa de desarrollo que incluye cristal de clock y polarización necesaria para su funcionamiento.

Figura 14 - Placa de desarrollo del sintetizador AD9850

Este sintetizador puede ser alimentado con 5V o 3.3V, y su salida tiene como mínimo 200mVPaP. Consume como máximo 96mA. Se encuentra disponible en pequeñas placas de desarrollo incluyendo cristales y otros componentes que facilitan su uso.

### 4.2.3 Mezcladores

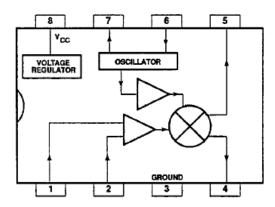

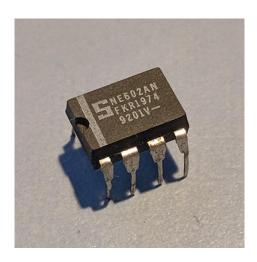

Los mezcladores deben poder funcionar con señales dentro del rango de trabajo, la frecuencia intermedia y banda base. El mezclador seleccionado NE602AN de Philips Semiconductors es un mezclador activo de baja potencia para frecuencias de VHF.

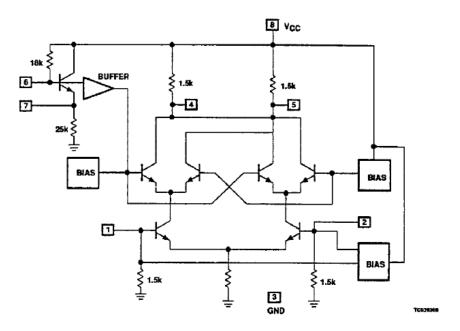

Figura 15 – Diagrama de bloques del NE602AN<sup>13</sup>

El mezclador NE602AN provee una ganancia típica de 18dB, puede configurarse con un cristal, circuito tanque o con oscilador externo. Tiene una baja figura de ruido. Se encuentra disponible en empaquetado DIP8 permitiendo su uso en protoboard, siendo esta una característica decisiva para la elección.

<sup>&</sup>lt;sup>13</sup> Imagen obtenida de datasheet del componente. Philips Semiconductors.

Figura 16 – NE602AN empaquetado DIP

La señal de entrada de este mezclador puede llegar hasta 500MHz y es capaz de recibir señales de hasta -119dBm. Tiene punto de intercepción de tercer orden aproximado de -13dBm. Se alimenta con 5V y consume típicamente 2,4mA. No requiere ningún tipo de polarización especial para sus entradas, de hecho, las señales deben ingresar filtradas por un capacitor para no contener componente continua. Su alimentación también debe ser filtrada para evitar que la señal escape por ahí.

Figura 17 – Circuito Equivalente del NE602AN<sup>14</sup>

<sup>&</sup>lt;sup>14</sup> Imagen obtenida de datasheet del componente. Philips Semiconductors.

### DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR

### BANCHIO, Agustín Enrique

Como se observa en el circuito equivalente, los pines 4 y 5 que contienen la salida del mezclador se encuentran polarizados con un resistor de  $1,5k\Omega$  conectado a la fuente de alimentación, y de conectar alguno de estos pines a tierra, se produciría un cortocircuito a tierra y el mezclador dejaría de funcionar. Además el pin 6 de la entrada del oscilador no puede ir a tierra, aunque el pin 7 sí, es decir, la entrada del oscilador no es simétrica como lo es la entrada de RF y la salida de IF.

### 4.2.4 Amplificadores

Existen una amplia gama de amplificadores monolíticos que trabajan en el rango de frecuencias requerido para este proyecto.

Entre ellos se seleccionaron MAR-3+ y, posteriormente, MAR-1+ de MiniCircuits, las características más importantes de cada uno son las siguientes:

#### o MAR-3+:

- Rango desde CC a 2GHz

- Ganancia típica de 12,5dB

- Compensado internamente para 50 Ohms

- Figura de ruido de 3,7dB

- Incondicionalmente estable

- Tensión de Operación 5V, Corriente 35mA

- Potencia de salida en punto de 1dB de compresión 10dBm

- Punto de intercepción de tercer orden (salida) 23dBm

#### o MAR-1+:

- Rango desde CC a 1GHz

- Ganancia típica de 17,8dB

- Compensado internamente para 50 Ohms

- Figura de ruido de 3,5dB

- Incondicionalmente estable

- Tensión de Operación 5V, Corriente 17mA

- Potencia de salida en punto de 1dB de compresión 2.5dBm

- Punto de intercepción de tercer orden (salida) 14dBm

Figura 18 – Amplificadores MAR-1 (izquierda) y MAR-3 (Derecha)

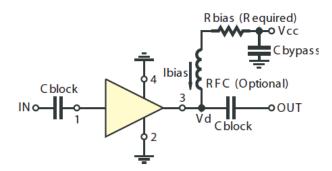

Ambos se encuentran en encapsulado de montaje superficial VV105. Se alimentan por el pin de salida de RF por lo que es necesario un inductor de choque. El fabricante recomienda colocar una resistencia para limitar la corriente y aplicar una tensión mayor de por lo menos 7V.

Figura 19 – Circuito recomendado de aplicación de amplificadores MAR según fabricante. <sup>15</sup>

Debido a que el amplificador MAR-1 tiene una ganancia típica mayor, una figura de ruido menor y un consumo menor, se lo consideró superior para este caso de uso con respecto al MAR-3. La razón de su elección es su bajo ruido, su amplia ganancia, su frecuencia de trabajo y que es incondicionalmente estable.

Para la amplificación en banda base se seleccionaron amplificadores operacionales los cuales, mediante jumpers, se pueden desactivar o activar variando así la amplificación de banda base.

<sup>&</sup>lt;sup>15</sup> Imagen obtenida de datasheet del componente. Mini-Circuits.

### DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR

BANCHIO, Agustín Enrique

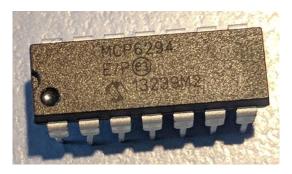

Los amplificadores operacionales seleccionados fueron MCP6294 de Microchip por sus características rail-to-rail, slew rate, y GBP. Se incluyen 4 amplificadores operacionales por encapsulado.

Figura 20 – MCP6294 encapsulado DIP

Entre las características del MCP6294 se destacan:

- o Rail-to-Rail en entrada y salida

- o Gain Bandwidth Product de 10MHz

- Consumo de corriente típico de 1mA

- Slew Rate 7V/uS

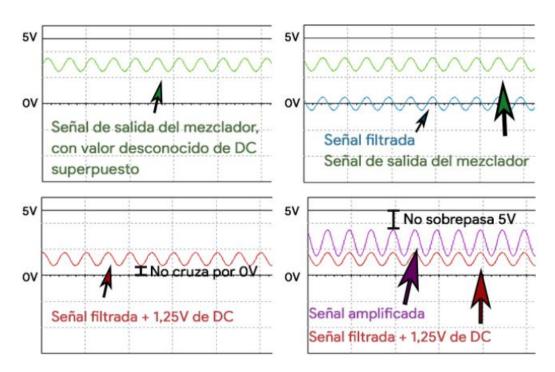

La señal obtenida a la salida del mezclador tiene una amplitud esperada calculable con las ganancias de los distintos componentes, pero superpuesta a una continua de valor no conocido (la salida máxima no será superior a la alimentación). Con los niveles de amplificación del circuito se espera una salida aproximada menor a 200mVpp.

Para amplificar la señal, se incluye un capacitor para filtrar la tensión continua antes de cada amplificador operacional, y luego se le suma un nivel de tensión conocido equivalente a un cuarto del valor de tensión de alimentación (1,25V para 5V de alimentación), que es suficientemente mayor que la amplitud de la señal. De esta manera los valles de la señal no cruzan por cero y toda la señal se mantiene en valores positivos, y cuando se duplica su amplitud tampoco se supera la tensión de alimentación (5V) y no se pierde información de la señal ni por corte ni por saturación.

Figura 21 – Amplificación de la señal sin sufrir distorsión por corte o saturación

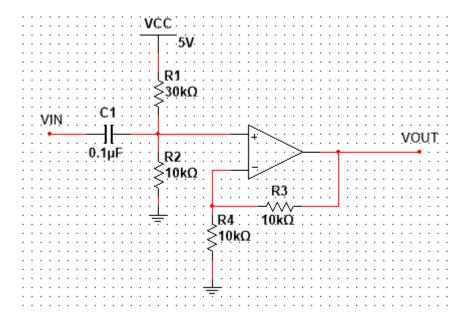

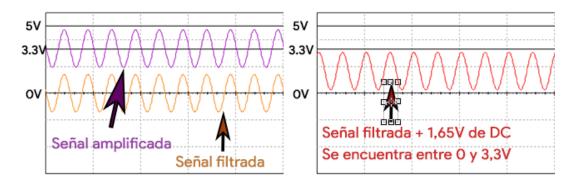

Figura 22 – Circuito que filtra la señal continua, le suma un cuarto de la tensión de alimentación y amplifica por dos.

El mismo procedimiento para amplificar la señal se realiza con amplificadores alimentados con 3,3V y escalando los valores de tensión correspondientemente.

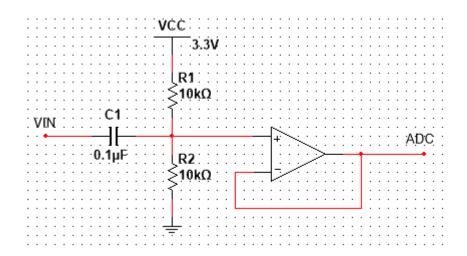

Previo a la entrada del ADC, la componente continua desconocida de la señal es eliminada y al resultado se le suma la mitad de la tensión de referencia del ADC, de manera de colocar la señal en el medio del rango de valores del conversor. El ADC utiliza 3,3V de referencia, por lo que el valor de tensión a sumar es 1,65V.

Figura 23 – Señal filtrada y desplazada al centro del rango del ADC

Figura 24 – Circuito que filtra la señal y le suma la mitad de la tensión de referencia, incluyendo un buffer previo al ADC

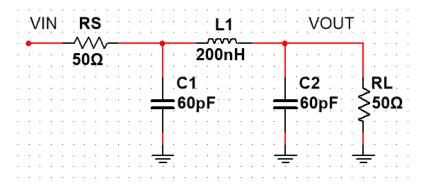

### 4.2.5 Filtros

En este trabajo, se implementaron 4 tipos de filtros.

O Un filtro para la etapa de RF, ubicado después del primer amplificador que filtra las frecuencias fuera del rango de trabajo del dispositivo.

- Un filtro para la etapa de IF, de tipo cerámico que filtra un pequeño ancho de banda y brinda mayor selectividad.

- O Un filtro para la etapa de Banda Base que elimina altas frecuencias que pueden encontrarse a la salida del mezclador.

- Dos filtros pasa bajos a la salida de los osciladores para eliminar ruidos de mayores frecuencias producidos por los sintetizadores

A continuación se analiza cada tipo de filtro con más detalle.

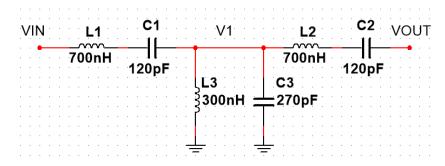

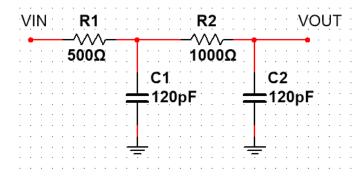

### 4.2.5.1 Filtro de la etapa de RF

Figura 25 – Diagrama esquemático del filtro de la etapa de RF

El objetivo de este filtro es que las señales de frecuencias inferiores a 10MHz y las superiores a 30MHz sean fuertemente atenuadas para no producir interferencia por frecuencia imagen.

Función de transferencia:

Si

$$C2 = C1$$

y  $L2=L1$

$$H(s) = \frac{Vout(s)}{Vin(s)}$$

$$Vout(s) = \frac{V_1(s).RL}{Z_{L1} + Z_{C1} + RL}$$

$$V_1(S) = \frac{\left(Vin(s).\left((Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL)\right)\right)}{(Z_{L1} + Z_{C1} + \left((Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL)\right)\right)}$$

$$Vout(S) = \frac{\left(Vin(s).\left((Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL)\right)\right)}{(Z_{L1} + Z_{C1} + \left((Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL)\right)\right)}.RL$$

$$Vout(S) = \frac{\left(Z_{L1} + Z_{C1} + \left((Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL)\right)\right)}{Z_{L1} + Z_{C1} + RL}$$

### DISEÑO E IMPLEMENTACIÓN DE FRONT END ANALÓGICO PARA SDR

BANCHIO, Agustín Enrique

$$H(S) = \frac{\left( (Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL) \right). RL}{(Z_{L1} + Z_{C1} + \left( (Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL) \right). (Z_{L1} + Z_{C1} + RL)}$$

Teniendo en cuenta que:

$$Z_{L} = L.S$$

$$Z_{C} = \frac{1}{C.S}$$

$$\left( (Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL) \right) = \frac{1}{\frac{1}{Z_{L3}} + \frac{1}{Z_{C3}} + \frac{1}{Z_{L1} + Z_{C1} + RL}}$$

$$\left( (Z_{L3}) \parallel Z_{C3} \parallel (Z_{L1} + Z_{C1} + RL) \right) = \frac{1}{\frac{1}{L3.S} + C3.S + \frac{1}{L1.S + \frac{1}{C1.S} + RL}}$$

$$H(S) = \frac{\frac{1}{\frac{1}{L3.S} + C3.S + \frac{1}{L1.S + \frac{1}{C1.S} + RL}}.RL}{\left(L1.S + \frac{1}{C1.S} + \frac{1}{\frac{1}{L3.S} + C3.S + \frac{1}{L1.S + \frac{1}{C1.S} + RL}}\right).\left(L1.S + \frac{1}{C1.S} + RL\right)}$$

H(S) =

$S^3.L3.C1^2.RL$

$\overline{S^{6}.L1^{2}.L3.C1^{2}.C3+S^{5}.L1.L3.C1^{2}.C3.RL+S^{4}.L1.C1.\big(L1.C1+2.L3.(C1+C3)\big)+S^{3}.C1.RL.\big(L1.C1+L3.(C1+C3)\big)+S^{2}.\big(2.L1.C1+L3.(2.C1+C3)\big)+S.C1.RL+1}$

$$Si\ RL = 50\ \Omega,\ C1 = 120pF,\ L1 = 700nH,\ L3 = 300nH\ y\ C3 = 270pF$$

$$H(S) = \frac{2,16.10^{-25}.S^3}{5,71536.10^{-49}.S^6 + 4,0824.10^{-41}.S^5 + 2,6712.10^{-32}.S^4 + 1,206.10^{-24}.S^3 + 3,21.10^{-16}.S^2 + 6.10^{-9}.S + 1}$$

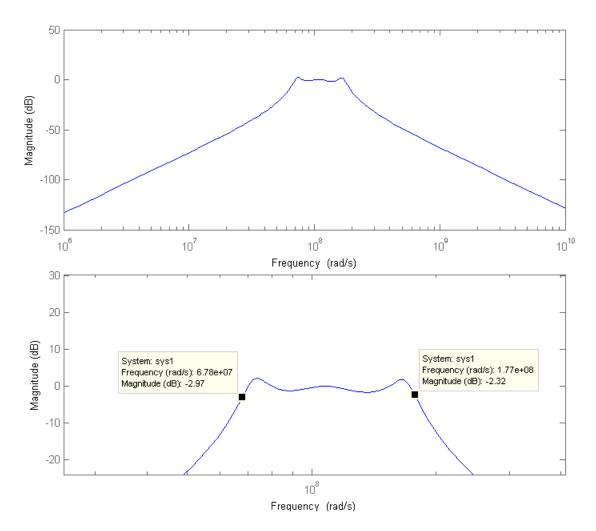

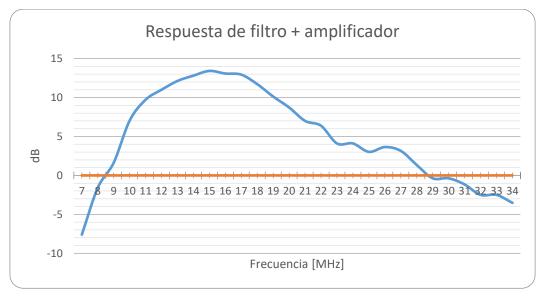

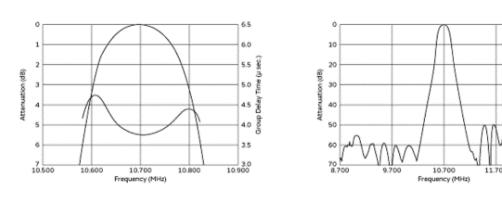

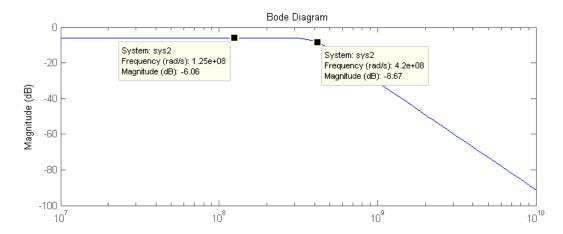

Figura 26 – Diagrama de Bode del filtro de la etapa de RF

Como se observa en el diagrama de Bode del filtro, éste se comporta como pasabanda con frecuencias de corte aproximadamente entre 10,79 MHz y 28,17 MHz, siendo estos valores cercanos a los deseados.

Figura 27 – Respuesta del filtro según simulación

Los resultados de simulación dan una respuesta similar al análisis matemático y al esperado.

Figura 28 – Respuesta de mediciones del filtro junto a un amplificador MAR-3+

Las mediciones realizadas del filtro junto a un amplificador muestran una respuesta asimétrica dentro del rango de trabajo del equipo, amplificando más frecuencias entre 9MHz y 22MHz, aún así se observa que la banda de paso del filtro es similar a la

esperada, y ya que su principal uso es atenuar señales fuera del rango de trabajo para evitar la frecuencia imagen, se lo consideró aceptable. Las diferencias entre las mediciones y los valores calculados probablemente se deban a las imperfecciones de los componentes utilizados. Se utilizaron capacitores e inductores fijos con distintos valores de tolerancia.

### 4.2.5.2 Filtro de la etapa de IF

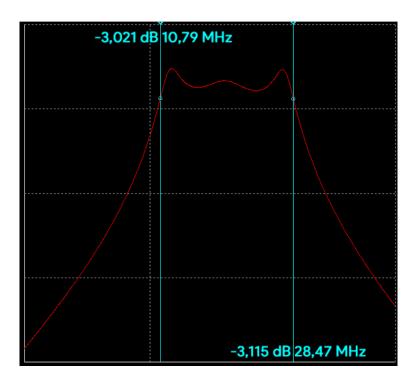

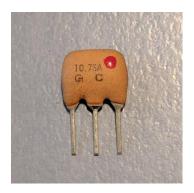

El filtro de la frecuencia intermedia utilizado es un filtro SFELF10M7HAA0-B0 de muRata de encapsulado cerámico.

Figura 29 – Filtro cerámico SFELF10M7HAA0-B0

Figura 30 – Respuesta del filtro cerámico<sup>16</sup>

El ancho de banda de este filtro es de 180KHz con frecuencia central en 10,7MHz y tiene una pérdida de inserción máxima de 7dB. Se seleccionó este filtro por su formato de agujero pasante y determinó la primera frecuencia intermedia en 10,7 MHz

<sup>&</sup>lt;sup>16</sup> Imagen obtenida de datasheet del componente. muRata.

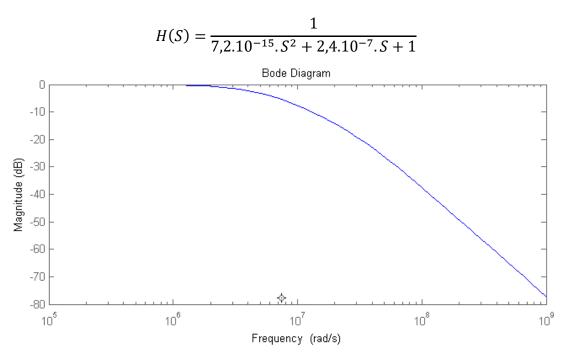

### 4.2.5.3 Filtro de la etapa de banda base

Figura 31 – Diagrama esquemático del filtro de la etapa de banda base

El objetivo del filtro es que las señales de frecuencias superiores a las que se quieren mostrar (180KHz) sean atenuadas, en especial las del oscilador e IF (10,7MHz). Es un filtro RC pasa bajo de segundo orden.

Función de transferencia:

$$H(S) = \frac{Vout(S)}{Vin(S)}$$